In the realm of wireless communication, autonomous vehicles, surveillance, and tracking systems, the performance of fractional-N phase locked loops (PLLs) plays a critical role. The presence of unwanted signals known as fractional spurs has long been a challenge in many modern radar systems and wireless transceivers. These issues have spurred scientists from Tokyo Tech to develop innovative design techniques aimed at tackling these problems and improving overall system performance.

One of the main enemies in fractional-N PLLs is jitter and fractional spurs. Jitter refers to the deviation from the ideal timing of the synthesized oscillation, while fractional spurs are unwanted signals that arise from errors in the system. These issues can significantly impact the phase noise in the output of the PLL, degrading overall system performance.

Led by Professor Kenichi Okada, a research team from Tokyo Tech set out to address these challenges by developing two innovative design techniques to create a low-spur fractional-N PLL. These techniques aim to minimize fractional spurs and improve the performance of PLLs used in various applications such as self-driving vehicles, target tracking systems, and remote sensors.

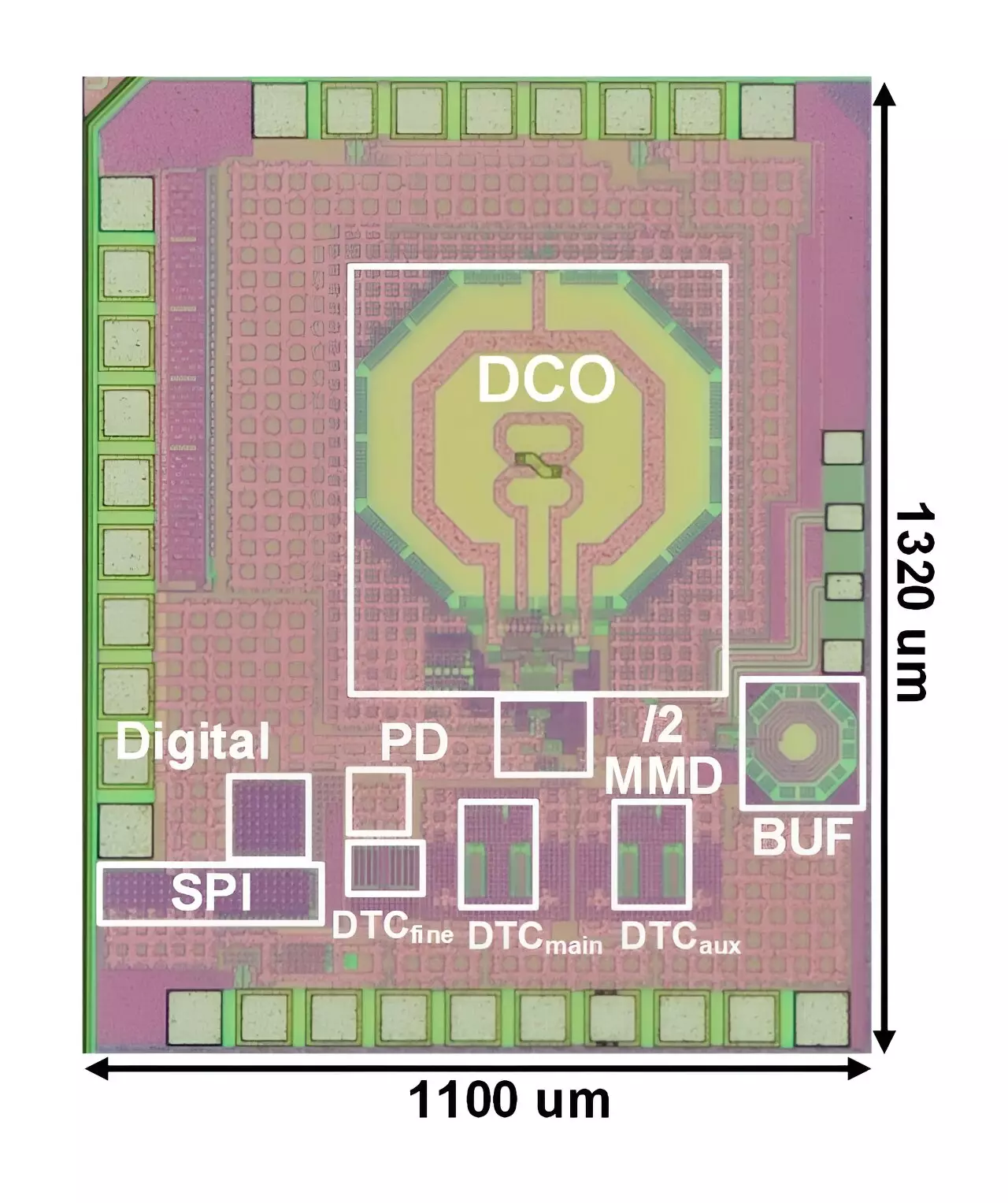

The first proposed technique involves the use of a cascaded-fractional divider. By splitting the frequency control word (FCW) into two values that are far from an integer, the researchers were able to reduce fractional spurs in the PLL at higher frequencies. This approach naturally filters out high-frequency components, without the complexity and slower phase locking associated with digital pre-distortion (DPD) techniques.

The second proposed technique focuses on a pseudo-differential DTC to overcome the limitations of standard DTC implementations. Conventional DTC designs often face trade-offs between power, delay range, noise, and integral non-linearities (INL) which can limit the achievable minimum fractional-spur level. By implementing a pseudo-differential DTC using two half-range DTCs with the same even-symmetric INLs in a differential operation, the researchers were able to cancel out these non-linearities at the PLL’s phase detector.

Read More: The Persistence of Landline Phones in a Digital Age

The research team implemented the proposed digital PLL using a 65 nm CMOS process, requiring a minimal active circuit area. By comparing the performance of their design with other state-of-the-art PLLs, the researchers observed significant improvements. The integrated PLL jitter was reduced from 243.5 fs to 143.7 fs by suppressing fractional spurs. The cascaded fractional divider and pseudo-differential DTC techniques allowed them to achieve a low level of jitter without the need for DPD technology.

The innovative design techniques developed by the research team at Tokyo Tech have the potential to revolutionize the performance of fractional-N PLLs in various applications. By minimizing fractional spurs and improving the overall performance of PLLs, these advancements could lead to technological improvements in wireless communication, autonomous vehicles, surveillance, and tracking systems. The quest for low-spur fractional-N PLLs continues as scientists work towards enhancing the reliability and efficiency of modern radar systems and wireless transceivers.

Leave a Reply